注意:XILINX ISE14.7 のインストール方法が変わりました !!!

【 1 】このTone Burst Converterの特徴

・ 基板の寸法が50 x 90ミリで 10Hz~100KHz の TONEをバースト・コントロールできます。

・ バースト(通過)する信号のダイナミックレンジは -5V ~ +5Vと広いです。

・ JTAG 端子をコネクタで出しておりますので、書込器があれば、別途提供いたします

ソースコード(VHDL)を変更して、バースト周期数と無信号周期数を変更することができます。

【 2 】 動作の説明

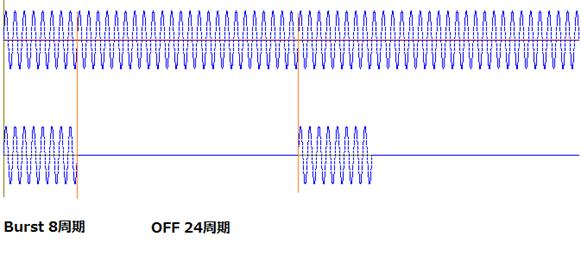

下図は、Burst 周期数が8で、無信号(OFF)周期数が24の場合で、その下の図 は、Burst 周期数

が3で、無信号(OFF)周期数が5です。 図の中の上の波形は入力信号、下の波形は出力信号です。

出荷時の設定は Burst 周期数:8、無信号(OFF)周期数:24となっており、これらの周期数

を変更するには、別途お渡しいたします ソースコード(VHDL)の定数を変更することで可能

です。

現在の設定は・・・

constant DAN : integer := 8; -- Burst number 通過させるサイクル数

constant DBN : integer := 24; -- Off number 通過させないサイクル数

・・・となっています。

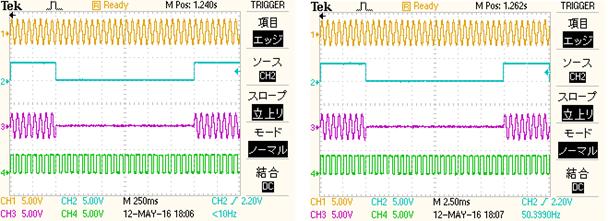

【 3 】実動作の波形

各周波数に対する入力信号、コントロール波形および出力信号の様子をオシロスコープ

で観測したものを下図に示します。

これらは全てBurst 周期数:8、無信号(OFF)周期数:24 のものです。

上から順に 入力信号・アナログ制御信号・出力信号・トリガ信号 となっています。

信号 16Hz 信号 1600Hz

信号 16KHz 信号 160KHz

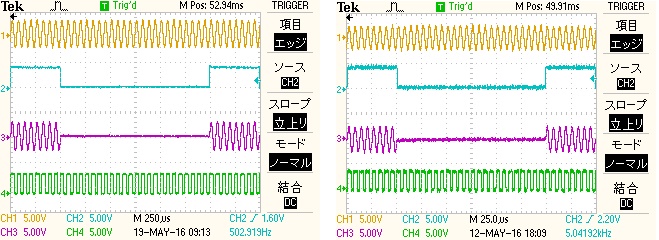

次に、バースト開始点と終了点を拡大して測定した図を示します。

バースト開始点の拡大

バースト終了点の拡大

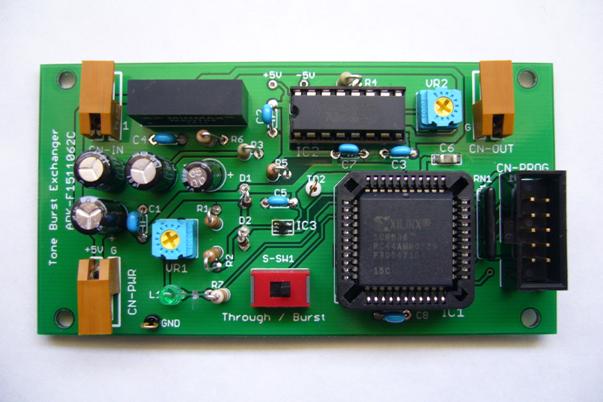

【 4 】実装基板写真

下図が実装した基板の写真です。

・ CN-INから入力信号を入れ、CN-OUTから出力信号を取り出します。

・ CN-PWRから電源を供給します。電圧は5Vで、1PINがプラスです。

・ CN-PROGはCPLDをプログラムするためのJTAG信号を出しています。

・ VR1は入力信号からクロック(トリガ)を取り出すときのバイアスを調整します。

・ VR2は出力信号のレベルを調整します。

・ L1 (LED)は、入力信号にトリガ が掛かったときに点灯します。

・ S-SW1(スライドSW)は、左側が全信号通過を指定し、右側で Burstを指定します。

電源の電圧や極性を間違えると故障いたしますので御留意ください。

JTAGの信号名(TCK,TDO,TDI,TMS,GND) については、下記の回路図を参照してください。

【 5 】回路図

【 6 】プログラミング

提供させていただいている ToneBurst12.vhdとToneBurst12.ucf ファイルを準備してください。Xilinx 社の ISEを起動して、メニューの File – New Project… をクリックします。

この ISE のバージョンは 10.1 で説明しますが、バージョンは違ってもほぼ同様な操作で作業できると思います。

Project location にプロジェクトを置く場所を指定し(任意です)、次に Project name を入力します。ここでは、Test とします。 すると Project location の後ろに Test が入ります。

つまり、ホルダ名がProject名と同じになることに注意して、たとえばこれを ToneBurst12 とする事もできますが 、ここではTestのままで続けます。 Next > をクリックします。

デバイスを上記の様に選択し Next > をクリックします。

ここではソースを新しく制作しませんから、そのまま Next > をクリックします。

後で追加します。ここではソースを追加しません。そのまま Next > をクリックします。

確認です。良ければ Finish をクリックします。

Source 窓のXc9536-15PC44 を右クリックして Add Source… をクリックします。

新しくできている「Test」ホルダに準備しているToneBurst12.vhdとToneBurst12.ucf ファイルを入れて、この2つのファイルを選択(Ctrlを押したままそれぞれのファイルをクリック)して「開く」をクリックします。

上図の確認画面が出てOKをクリックすると・・・

プロジェクトにファイルが取り込まれます。ToneBurst12 – RTL(ToneBurst12.vhd) をダブルクリックすると、右側にそのソースのエディタが出ます。バーストサイクル数と無信号サイクル数を変更するには・・・

constant DAN : integer := 8; -- Burst number 通過させるサイクル数

constant DBN : integer := 24; -- Off number 通過させないサイクル数

・・・この数値を書き換えます。

メニューの Process – Implement Top Module を実行するか右上の朱角のマークをクリックするとImplement 動作が始まります。

上図のように Processes 窓の Implement Design のGenerale Programming Fileのチェックが緑となれば成功です。これでホルダ内には ToneBurst12.jed (書き込み用)ファイルができていますから、これを書込器から指定して書き込めばOKです。

上図は、書き込み時のセッティングの例です。

日本語でここまでの詳しい解説はそうはありません。ありがとうございます!

【 XILINX ISE 14.7 のインストールについて 】

2023,5,10 インストール方法が変わりました !!!

従来のインストール法で動作している ISE14.7 が、当方に 3台ありました。下記の通りです。

1. Windows10 32bit ディスクトップ(Core i5)

2. Windpws10 64bit ディスクトップ(Core i5)

3. Windows11 Pro Note (Core i7)

この内、1.以外は動かなくなりました。つまり、OS_32bit のものは動作しているが 64bit では起動しなくなったのです。OS_64bit で ISE14.7 を最後に稼働させてから、一年以上、使っていませんでしたが久しぶりに使用しようと起動しましたが、まったく起動そのものができなくなっていました。

これは困ったものだと WEB で検索しましたところ、同じような方がおられて、投稿を見つけました。

(1) 【回路設計ヒント】Microsoft Windows 10 でのiMPACT書き込み

(2) Windows 10 用 ISE Design Suite – 14.7 をインストール

どちらの方もWindows11でも使ってあるようです。下の方のリンクは、上の方のリンクを参考にインストールされています。ただし、古いパソコンでもインストールすることができるように、追加の解説があります。いずれにしても、「仮想マシン上にISEをインストールして使用する」というやりかたで、そのための ISE14.7 のインストーラも「Xilinx_ISE_14.7_Win10_14.7_VM_0213_1.zip」という名称で出ているようです。つまり、Windows10 64bit, Womdpws11 で、ISE14.7 が動作しないような仕様に変わったので、仮想マシン上で稼働させる、新しいやり方のインストーラが提供されたのだと思います。

OS_64bit のパソコンを (2) のリンクを参考にして、 ISE14.7 を動作させることができました。この記事をアップして戴いた御二方に感謝申し上げます、誠にありがとうございました。Windows10 64bit でも Windows11 でも、 ISE14.7 を稼働し、iMPACT で書き込みもできるようになりました。

注意点として、仮想マシン上で稼働させると、ISE14.7 や iMPACT からは、ISE14.7 をインストールする時に指定したフォルダのファイルしか見えません。従来、プロジェクトはパソコン内のどこにでも置け、プロジェクトの「*.xise」をダブルクリックすれば、そのプロジェクトが立ち上がりました。しかし、今後は、そのようにはできません。

ISE14.7 のインストール時に「Select Destination Directry」タブ内の「Select the directory to share with VM」で指定したフォルダ内のファイルしか見えません。これをリンク(1) の中では、「C:\hogemoge」と書いてあります。私は「C:\X_ISE_VM」といたしました。その上で、これまで制作してきたプロジェクトをフォルダ込み、このフォルダに移動すると良いと思います。そうすれば、ISE14.7 や iMPACT から、それらの全てのファイルが見えるようになります。

追加情報

Windows11 Pro が、アップデートされた時に、Oracle VM VirtualBox は起動できるのですが、ISE_14.7_VIRTUAL_MACHINE が起動できなくなりました。エラーメッセージは・・・

仮想マシン"ISE_14.7_VIRTUAL_MACHINE"のセッションを開けませんでした。

Interface ('VirtualBox Host-Only Ethernet Adapter') is not a Host-Only Adapter interface (VERR_INTERNAL_ERROR).

終了コード : E_FAIL (0x80004005)

・・・というものです。詳しい理由はわからないのですが、次の設定で、起動できるようになりました。

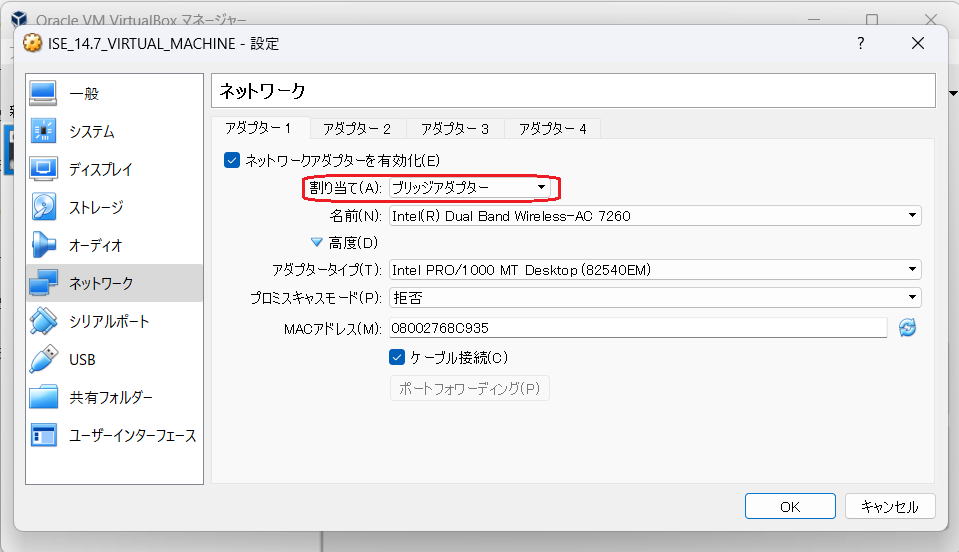

つまり、Oracle_VM VirtualBox マネージャの設定から「ネットワーク」を選択して、「ネットワークアダプタの有効化」の「割り当て」 が「ホストオンリーアダプタ」となっているのをドロップダウンリストから「ブリッジアダプタ」に変更しました。これで起動できました。下図の通りです。

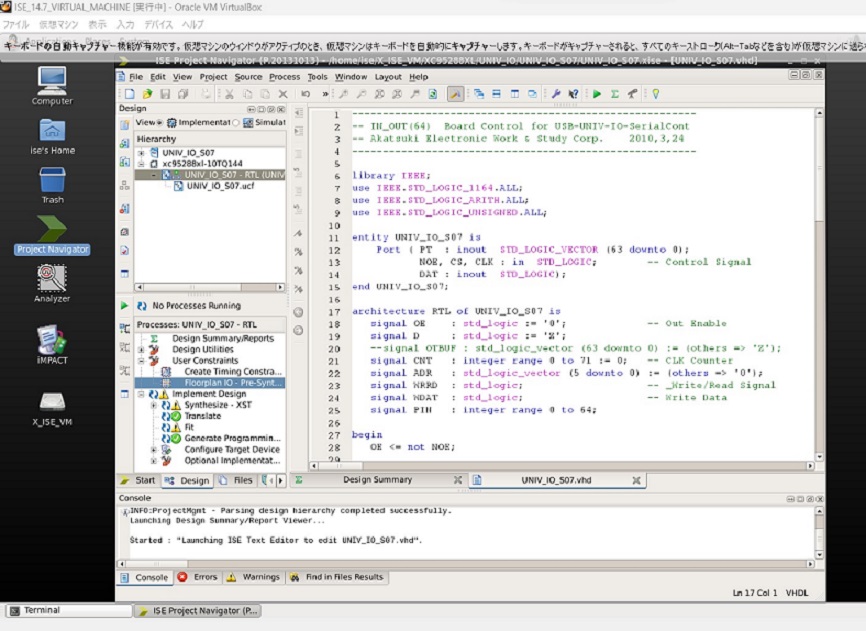

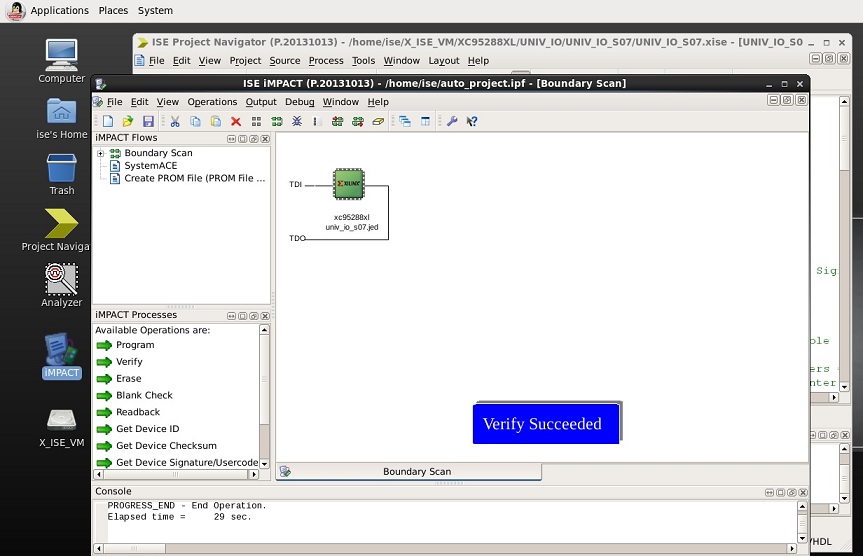

以下の図は、動作画面です。

仮想マシン上での ISE14.7 の 稼働状況

仮想マシン上での iMPACT の稼働状況

下記の旧解説は、Windows10 32bit までは有効だと思いますので残しておきます。

============== 旧解説 ==============

Windows10 で ISE 14.7 を動作させるには、以下のリンクに詳しい解説があります。

OSが64ビットでの解説です、32ビットの場合は、ホルダ名"nt64"を"nt"に読み替えれば良い

ようです。このバージョンでは従来のプロジェクトを読み込むと拡張子が、.ise から .xise に変

更 されます。

ISIMが起動しない・・・については下記リンクを参考にしてください。

http://openit.kek.jp/training/2014/fpga/docs/Windows8_trouble.pdf ・・ ありがとうございます。

提供致していますソースによる移植は、ほぼ上記で解説した手順でプロジェクトを制作すること

が確認できました。

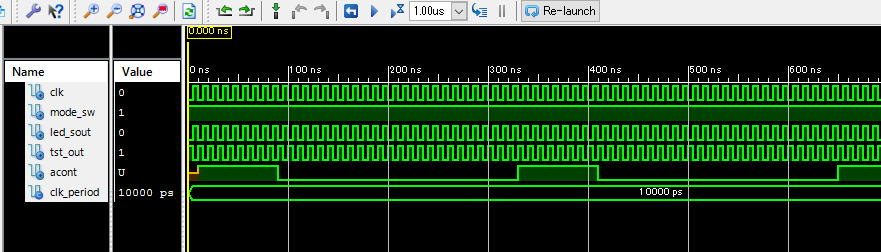

下図は、ISIMによる確認の様子です。

ToneBurst通販のページ

戻 る